# <u>UNIT-I</u>

# PN JUNC<mark>TI</mark>ON DIODE

# **INTRODUCTON**

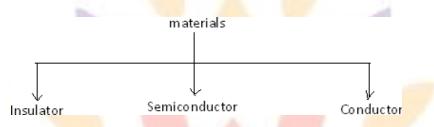

Based on the electrical conductivity all the materials in nature are classified as insulators, semiconductors, and conductors.

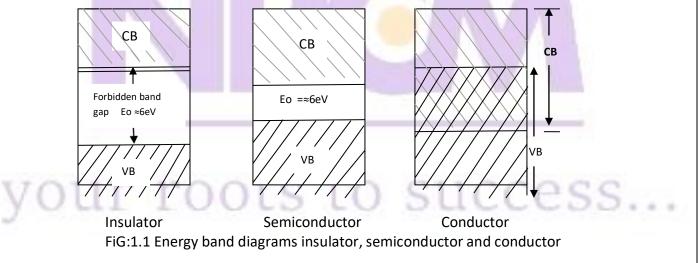

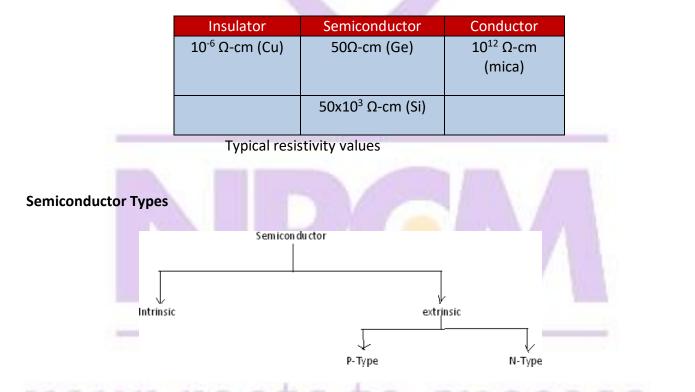

**Insulator**: An insulator is a material that offers a very low level (or negligible) of conductivity when voltage is applied. Eg: Paper, Mica, glass, quartz. Typical resistivity level of an insulator is of the order of  $10^{10}$  to  $10^{12} \Omega$ -cm. The energy band structure of an insulator is shown in the fig.1.1. Band structure of a material defines the band of energy levels that an electron can occupy. Valance band is the range of electron energy where the electron remain bended too the atom and do not contribute to the electric current. Conduction bend is the range of electron energies higher than valance band where electrons are free to accelerate under the influence of external voltage source resulting in the flow of charge.

The energy band between the valance band and conduction band is called as forbidden band gap. It is the energy required by an electron to move from balance band to conduction band i.e. the energy required for a valance electron to become a free electron.

1 eV = 1.6 x 10<sup>-19</sup> J

For an insulator, as shown in the fig.1.1 there is a large forbidden band gap of greater than 5Ev. Because of this large gap there a very few electrons in the CB and hence the conductivity of insulator is poor. Even an increase in temperature or applied electric field is insufficient to transfer electrons from VB to CB.

**Conductors:** A conductor is a material which supports a generous flow of charge when a voltage is applied across its terminals. i.e. it has very high conductivity. Eg: Copper, Aluminum, Silver, Gold. The resistivity of a conductor is in the order of  $10^{-4}$  and  $10^{-6}$   $\Omega$ -cm. The Valance and conduction bands overlap (fig1.1) and there is no energy gap for the electrons to move from valance band to conduction band. This implies that there are free electrons in CB even at absolute zero temperature (OK). Therefore at room temperature when electric field is applied large current flows through the conductor.

**Semiconductor**: A semiconductor is a material that has its conductivity somewhere between the insulator and conductor. The resistivity level is in the range of 10 and  $10^4 \Omega$ -cm. Two of the most commonly used are Silicon (Si=14 atomic no.) and germanium (Ge=32 atomic no.). Both have 4 valance electrons. The forbidden band gap is in the order of 1eV. For eg., the band gap energy for Si, Ge and GaAs is 1.21, 0.785 and 1.42 eV, respectively at absolute zero temperature (OK). At OK and at low temperatures, the valance band electrons do not have sufficient energy to move from V to CB. Thus semiconductors act a insulators at OK. as the temperature increases, a large number of valance electrons acquire sufficient energy to leave the VB, cross the forbidden bandgap and reach CB. These are now free electrons as they can move freely under the influence of electric field. At room temperature there are sufficient electrons in the CB and hence the semiconductor is capable of conducting some current at room temperature.

Inversely related to the conductivity of a material is its resistance to the flow of charge or current. Typical resistivity values for various materials' are given as follows.

A pure form of semiconductors is called as intrinsic semiconductor. Conduction in intrinsic sc is either due to thermal excitation or crystal defects. Si and Ge are the two most important semiconductors used. Other examples include Gallium arsenide GaAs, Indium Antimonide (InSb) etc.

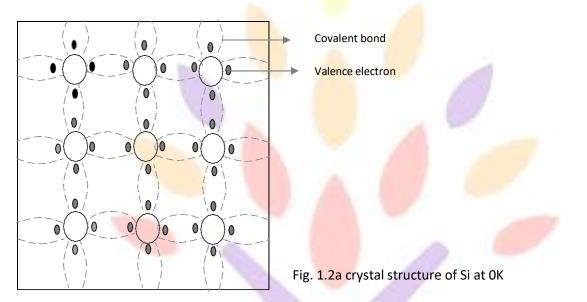

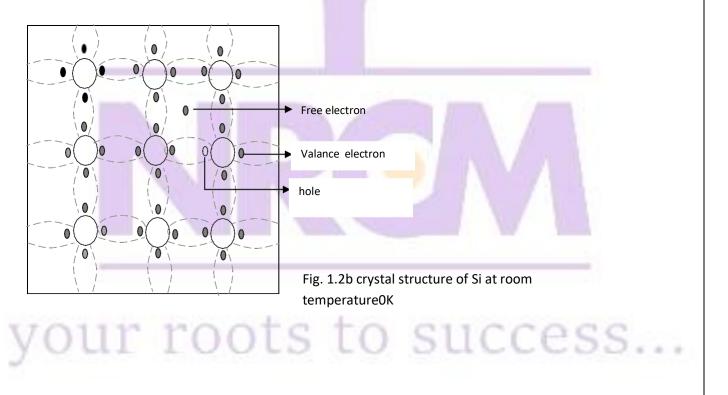

Let us consider the structure of Si. A Si atomic no. is 14 and it has 4 valance electrons. These 4 electrons are shared by four neighboring atoms in the crystal structure by means of covalent bond. Fig. 1.2a shows the crystal structure of Si at absolute zero temperature (OK). Hence a pure SC acts has poor conductivity (due to lack of free electrons) at low or absolute zero temperature.

At room temperature some of the covalent bonds break up to thermal energy as shown in fig 1.2b. The valance electrons that jump into conduction band are called as free electrons that are available for conduction.

The absence of electrons in covalent bond is represented by a small circle usually referred to as hole which is of positive charge. Even a hole serves as carrier of electricity in a manner similar to that of free electron.

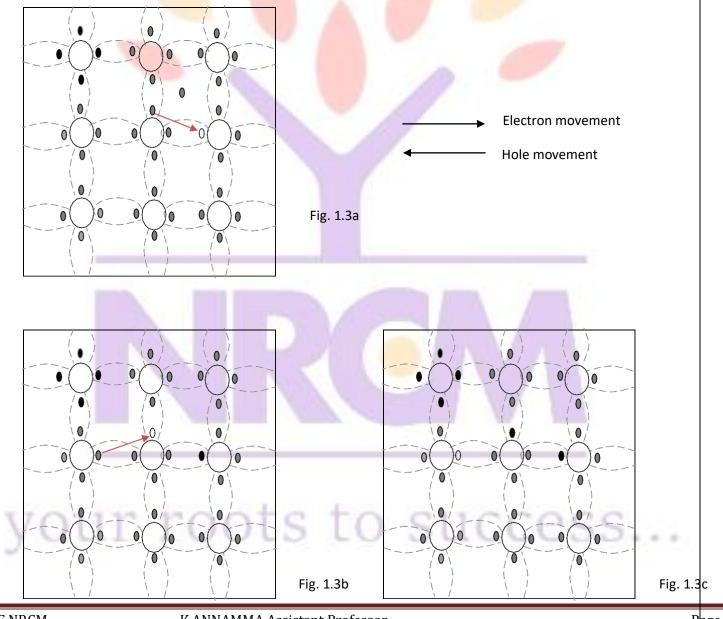

The mechanism by which a hole contributes to conductivity is explained as follows:

When a bond is in complete so that a hole exists, it is relatively easy for a valance electron in the neighboring atom to leave its covalent bond to fill this hole. An electron moving from a bond to fill a hole moves in a direction opposite to that of the electron. This hole, in its new position may now be filled by an electron from another covalent bond and the hole will correspondingly move one more step in the direction opposite to the motion of electron. Here we have a mechanism for conduction of electricity which does not involve free electrons. This phenomenon is illustrated in fig1.3

CSE,NRCM

Fig 1.3a show that there is a hole at ion 6.Imagine that an electron from ion 5 moves into the hole at ion 6 so that the configuration of 1.3b results. If we compare both fig1.3a &fig 1.3b, it appears as if the hole has moved towards the left from ion6 to ion 5. Further if we compare fig 1.3b and fig 1.3c, the hole moves from ion5 to ion 4. This discussion indicates the motion of hole is in a direction opposite to that of motion of electron. Hence we consider holes as physical entities whose movement constitutes flow of current.

In a pure semiconductor, the number of holes is equal to the number of free electrons.

#### **EXTRINSIC SEMICONDUCTOR**

Intrinsic semiconductor has very limited applications as they conduct very small amounts of current at room temperature. The current conduction capability of intrinsic semiconductor can be increased significantly by adding a small amounts impurity to the intrinsic semiconductor. By adding impurities it becomes impure or extrinsic semiconductor. This process of adding impurities is called as doping. The amount of impurity added is 1 part in 10<sup>6</sup> atoms.

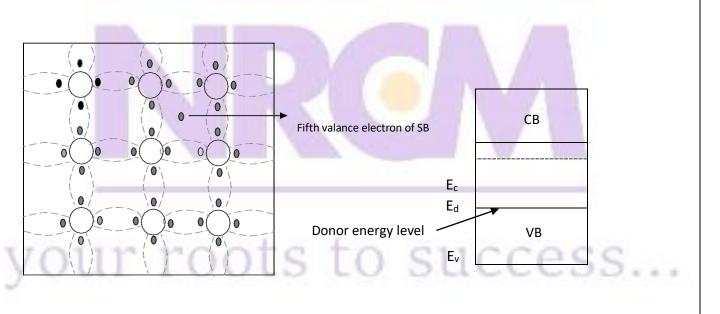

**N type semiconductor:** If the added impurity is a pentavalent atom then the resultant semiconductor is called N-type semiconductor. Examples of pentavalent impurities are Phosphorus, Arsenic, Bismuth, Antimony etc.

A pentavalent impurity has five valance electrons. Fig 1.4a shows the crystal structure of N-type semiconductor material where four out of five valance electrons of the impurity atom(antimony) forms covalent bond with the four intrinsic semiconductor atoms. The fifth electron is loosely bound to the impurity atom. This loosely bound electron can be easily

Fig. 1.4a crystal structure of N type SC

Fig. 1.4bEnergy band diagram of N type

Excited from the valance band to the conduction band by the application of electric field or increasing the thermal energy. The energy required to detach the fifth electron form the impurity atom is very small of the order of 0.01ev for Ge and 0.05 eV for Si.

The effect of doping creates a discrete energy level called donor energy level in the forbidden band gap with energy level  $E_d$  slightly less than the conduction band (fig 1.4b). The difference between the energy levels of the conducting band and the donor energy level is the energy required to free the fifth valance electron (0.01 eV for Ge and 0.05 eV for Si). At room temperature almost all the fifth electrons from the donor impurity atom are raised to conduction band and hence the number of electrons in the conduction band increases significantly. Thus every antimony atom contributes to one conduction electron without creating a hole.

In the N-type sc the no. of electrons increases and the no. of holes decreases compared to those available in an intrinsic sc. The reason for decrease in the no. of holes is that the larger no. of electrons present increases the recombination of electrons with holes. Thus current in N type sc is dominated by electrons which are referred to as majority carriers. Holes are the minority carriers in N type sc

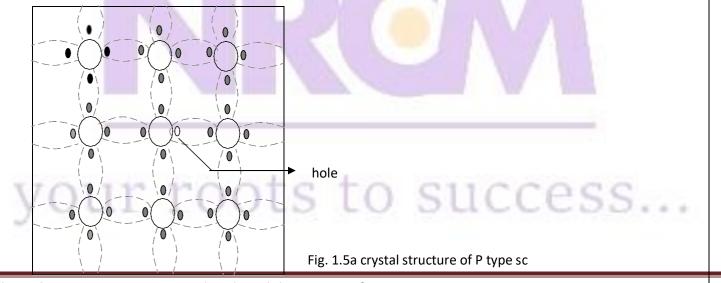

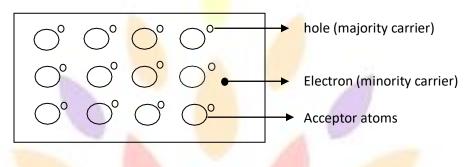

**P type semiconductor:** If the added impurity is a trivalent atom then the resultant semiconductor is called P-type semiconductor. Examples of trivalent impurities are Boron, Gallium , indium etc.

The crystal structure of p type sc is shown in the fig1.5a. The three valance electrons of the impurity (boon) forms three covalent bonds with the neighboring atoms and a vacancy exists in the fourth bond giving rise to the holes. The hole is ready to accept an electron from the neighboring atoms. Each trivalent atom contributes to one hole generation and thus introduces a large no. of holes in the valance band. At the same time the no. electrons are decreased compared to those available in intrinsic sc because of increased recombination due to creation of additional holes.

CSE,NRCM

Thus in P type sc , holes are majority carriers and electrons are minority carriers. Since each trivalent impurity atoms are capable accepting an electron, these are called as acceptor atoms. The following fig 1.5b shows the pictorial representation of P type sc

Fig. 1.5b crystal structure of P type sc

- The conductivity of N type sc is greater than that of P type sc as the mobility of electron is greater than that of hole.

- For the same level of doping in N type sc and P type sc, the conductivity of an Ntype sc is around twice that of a P type sc

#### CONDUCTIVITY OF SEMICONDUCTOR

In a pure sc, the no. of holes is equal to the no. of electrons. Thermal agitation continue to produce new electron- hole pairs and the electron hole pairs disappear because of recombination. with each electron hole pair created , two charge carrying particles are formed . One is negative which is a free electron with mobility  $\mu_n$ . The other is a positive i.e., hole with mobility  $\mu_p$ . The electrons and hole move in opppsitte direction in a an electric field E, but since they are of opposite sign, the current due to each is in the same direction. Hence the total current density J within the intrinsic sc is given by

$$J = J_n + J_p$$

$$= q n \mu_n E + q p \mu_p E$$

$$= (n \mu_n + p \mu_p)qE$$

$$= \zeta E$$

Where n=no. of electrons / unit volume i.e., concentration of free electrons

$$P = no. of holes / unit volume i.e., concentration of holes$$

$$E = applied electric field strength, V/m$$

$$q = charge of electron or hole I n Coulombs$$

CSE,NRCM

K.ANNAMMA,Assistant Professor

Page

Hence,  $\varsigma$  is the conductivity of sc which is equal to  $(n \mu_n + p \mu_p)q$ . he resistivity of sc is reciprocal of conductivity.

$P = 1/\varsigma$

It is evident from the above equation that current density with in a sc is directly proportional to applied electric field E.

For pure sc,  $n=p=n_i$  where  $n_i = intrinsic concentration$ . The value of  $n_i$  is given by

$n_i^2 = AT^3 \exp(-E_{GO}/KT)$

therefore,  $J = n_i (\mu_n + \mu_p) q E$

Hence conductivity in intrinsic sc is  $\varsigma i = n_i (\mu_n + \mu_p) q$

Intrinsic conductivity increases at the rate of 5% per ° C for Ge and 7% per ° C for Si.

#### Conductivity in extrinsic sc (N Type and P Type):

The conductivity of intrinsic sc is given by  $\varsigma i = n_i (\mu_n + \mu_p) q = (n \mu_n + p \mu_p)q$

For N type , n>>p

Therefore  $\varsigma = q n \mu_n$

For P type ,p>>n

Therefore  $\varsigma = q p \mu_p$

#### CHARGE DENSITIES IN P TYPE AND N TYPE SEMICONDUCTOR:

#### **Mass Action Law:**

Under thermal equilibrium for any semiconductor, the product of the no. of holes and the concentration of electrons is constant and is independent of amount of donor and acceptor impurity doping.

ts to success...

$n.p=n_i^2$

where n= electron concentration

p = hole concentration  $n_i^2 =$  intrinsic concentration

Hence in N type sc , as the no. of electrons increase the no. of holes decreases. Similarly in P type as the no. of holes increases the no. of electrons decreases. Thus the product is constant and is equal to  $n_i^2$  in case of intrinsic as well as extrinsic sc.

The law of mass action has given the relationship between free electrons concentration and hole concentration. These concentrations are further related by the law of electrical neutrality as explained below.

#### Law of electrical neutrality:

Sc materials are electrically neutral. According to the law of electrical neutrality, in an electrically neutral material, the magnitude of positive charge concentration is equal to tat of negative charge concentration. Let us consider a sc that has  $N_D$  donor atoms per cubic centimeter and  $N_A$  acceptor atoms per cubic centimeter i.e., the concentration of donor and acceptor atoms are  $N_D$  and  $N_A$  respectively. Therefore  $N_D$  positively charged ions per cubic centimeter are contributed by donor atoms and  $N_A$  negatively charged ions per cubic centimeter are contributed by the acceptor atoms. Let n, p is concentration of free electrons and holes respectively. Then according to the law of neutrality

$$N_D + p = N_A + n$$

.....eq 1.1

Hence for N type sc the free electron concentration is approximately equal to the concentration of donor atoms. In later applications since some confusion may arise as to which type of sc is under consideration a the given moment, the subscript n or p is added for Ntype or P type respectively. Hence eq1.2 becomes  $N_D \approx n_n$

Therefore current density in N type sc is  $J = N_D \mu_n q E$

And conductivity  $\varsigma = N_D \mu_n q$

For P type sc,  $N_D = 0$  and p>>n. Therefore  $N_A \approx p$

$Or \ N_A \approx p_p$

Hence for P type sc the hole concentration is approximately equal to the concentration of acceptor atoms.

s to success.

Therefore current density in N type sc is  $J = N_A \mu_p q E$

And conductivity  $\varsigma = N_A \mu_p q$

Mass action law for N type,  $n_n p_n = n_i^2$

$p_n = n_i^2 / N_D$  since  $(n_n \approx N_D)$

Mass action law for P type,  $n_p p_p = n^2$

$n_p = n_i^2 / N_A$  since  $(p_p \approx N_A)$

#### QUANTITATIVE THEORY OF PN JUNCTION DIODE

#### PN JUNCTION WITH NO APPLIED VOLTAGE OR OPEN CIRCUIT CONDITION:

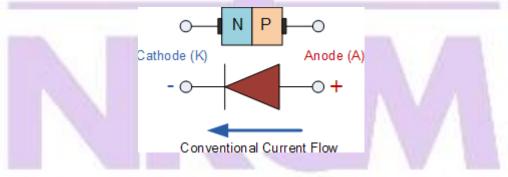

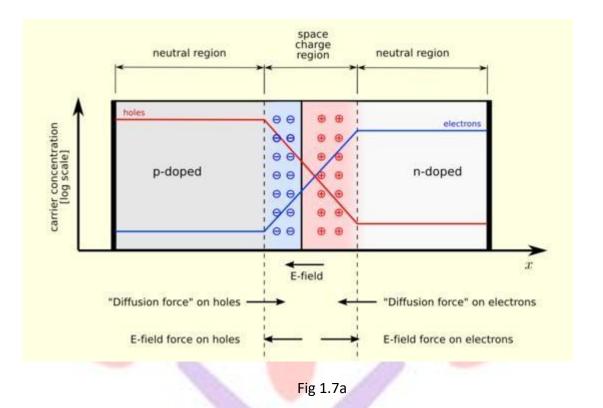

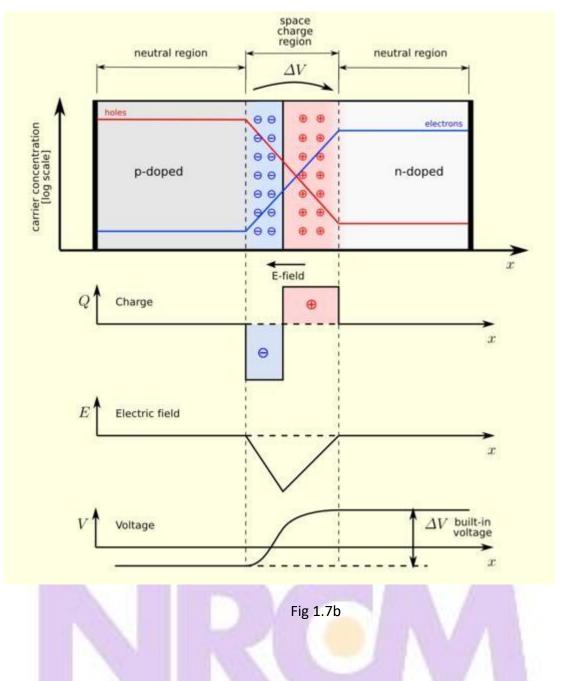

In a piece of sc, if one half is doped by p type impurity and the other half is doped by n type impurity, a PN junction is formed. The plane dividing the two halves or zones is called PN junction. As shown in the fig the n type material has high concentration of free electrons, while p type material has high concentration of free electrons, while p type material has high concentration of holes. Therefore at the junction there is a tendency of free electrons to diffuse over to the P side and the holes to the N side. This process is called diffusion. As the free electrons move across the junction from N type to P type, the donor atoms become positively charged. Hence a positive charge is built on the N-side of the junction. The free electrons that cross the junction uncover the negative acceptor ions by filing the holes. Therefore a negative charge is developed on the p –side of the junction. This net negative charge on the p side prevents further diffusion of electrons into the p side. Similarly the net positive charge on the N side repels the hole crossing from p side to N side. Thus a barrier sis set up near the junction which prevents the further movement of charge carriers i.e. electrons and holes. As a consequence of induced electric field across the depletion layer, an electrostatic potential difference is established between P and N regions, which are called the potential barrier, junction barrier, diffusion potential or contact potential, Vo. The magnitude of the contact potential Vo varies with doping levels and temperature. Vo is 0.3V for Ge and 0.72 V for Si.

Fig 1.6: Symbol of PN Junction Diode

The electrostatic field across the junction caused by the positively charged N-Type region tends to drive the holes away from the junction and negatively charged p type regions tend to drive the electrons away from the junction. The majority holes diffusing out of the P region leave behind negatively charged acceptor atoms bound to the lattice, thus exposing a negatives pace charge in a previously neutral region. Similarly electrons diffusing from the N region expose positively ionized donor atoms and a double space charge builds up at the junction as shown in the fig. 1.7a

It is noticed that the space charge layers are of opposite sign to the majority carriers diffusing into them, which tends to reduce the diffusion rate. Thus the double space of the layer causes an electric field to be set up across the junction directed from N to P regions, which is in such a direction to inhibit the diffusion of majority electrons and holes as illustrated in fig 1.7b. The shape of the charge density,  $\rho$ , depends upon how diode id doped. Thus the junction region is depleted of mobile charge carriers. Hence it is called depletion layer, space region, and transition region. The depletion region is of the order of 0.5µm thick. There are no mobile carriers in this narrow depletion region. Hence no current flows across the junction and the system is in equilibrium. To the left of this depletion layer, the carrier concentration is  $p = N_A$  and to its right it is  $n = N_D$ .

# your roots to success...

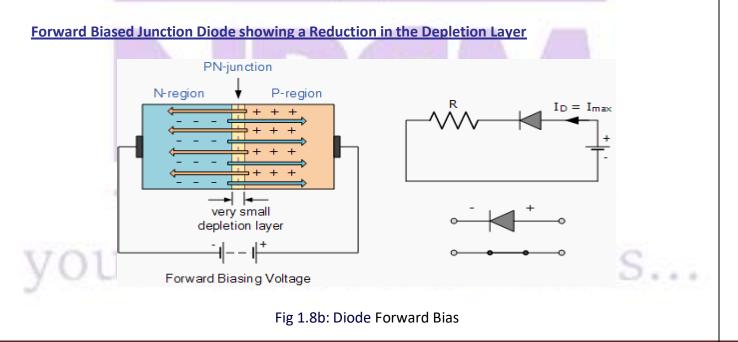

#### FORWARD BIASED JUNCTION DIODE

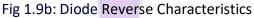

When a diode is connected in a **Forward Bias** condition, a negative voltage is applied to the Ntype material and a positive voltage is applied to the P-type material. If this external voltage becomes greater than the value of the potential barrier, approx. 0.7 volts for silicon and 0.3 volts for germanium, the potential barriers opposition will be overcome and current will start to flow. This is because the negative voltage pushes or repels electrons towards the junction giving them the energy to cross over and combine with the holes being pushed in the opposite direction towards the junction by the positive voltage. This results in a characteristics curve of zero current flowing up to this voltage point,

called the "knee" on the static curves and then a high current flow through the diode with little increase in the external voltage as shown below.

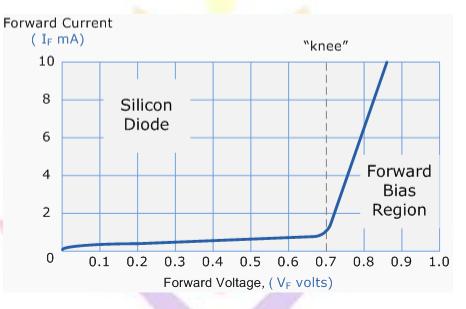

### Forward Characteristics Curve for a Junction Diode

Fig 1.8a: Diode Forward Characteristics

The application of a forward biasing voltage on the junction diode results in the depletion layer becoming very thin and narrow which represents a low impedance path through the junction thereby allowing high currents to flow. The point at which this sudden increase in current takes place is represented on the static I-V characteristics curve above as the "knee" point.

This condition represents the low resistance path through the PN junction allowing very large currents to flow through the diode with only a small increase in bias voltage. The actual potential difference across the junction or diode is kept constant by the action of the depletion layer at approximately 0.3v for germanium and approximately 0.7v for silicon junction diodes. Since the diode can conduct "infinite" current above this knee point as it effectively becomes a short circuit, therefore resistors are used in series with the diode to limit its current flow. Exceeding its maximum forward current specification causes the device to dissipate more power in the form of heat than it was designed for resulting in a very quick failure of the device.

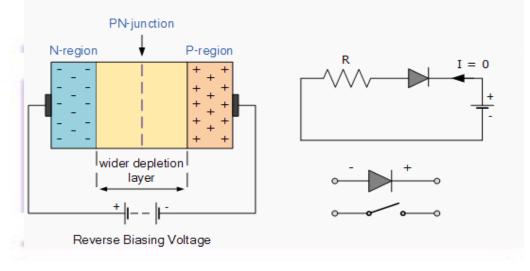

#### **1.1.2 PN JUNCTION UNDER REVERSE BIAS CONDITION:**

#### **Reverse Biased Junction Diode**

When a diode is connected in a **Reverse Bias** condition, a positive voltage is applied to the N-type material and a negative voltage is applied to the P-type material. The positive voltage applied to the N-type material attracts electrons towards the positive electrode and away from the junction, while the holes in the P-type end are also attracted away from the junction towards the negative electrode. The net result is that the depletion layer grows wider due to a lack of electrons and holes and presents a high impedance path, almost an insulator. The result is that a high potential barrier is created thus preventing current from flowing through the semiconductor material.

#### Reverse Biased Junction Diode showing an Increase in the Depletion

#### Fig 1.9a: Diode Reverse Bias

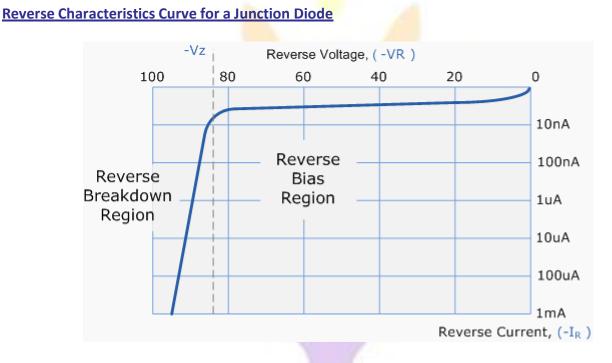

This condition represents a high resistance value to the PN junction and practically zero current flows through the junction diode with an increase in bias voltage. However, a very small **leakage current** does flow through the junction which can be measured in microamperes, ( $\mu$ A). One final point, if the

reverse bias voltage Vr applied to the diode is increased to a sufficiently high enough value, it will cause the PN junction to overheat and fail due to the avalanche effect around the junction. This maycause the diode to become shorted and will result in the flow of maximum circuit current, and this shown as a step downward slope in the reverse static characteristics curve below.

Sometimes this avalanche effect has practical applications in voltage stabilizing circuits where a series limiting resistor is used with the diode to limit this reverse breakdown current to a preset maximum value thereby producing a fixed voltage output across the diode. These types of diodes are commonly known as **Zener Diodes**

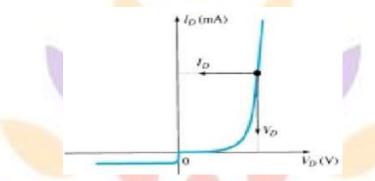

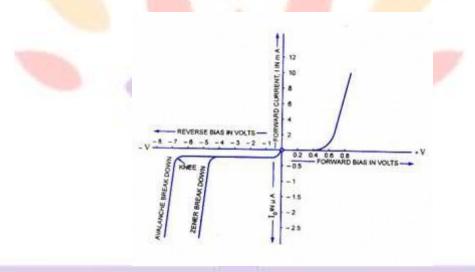

## VI CHARACTERISTICS AND THEIR TEMPERATURE DEPENDENCE

Diode terminal characteristics equation for diode junction current:

$$I_{D} = I_{0} (e^{\frac{v}{\eta v_{T}}} - 1)$$

Where  $V_T = KT/q$ ;

V<sub>D</sub> diode terminal voltage, Volts

# your roots to success..

#### Fig 1.10: Diode Characteristics

#### **Temperature Effects on Diode**

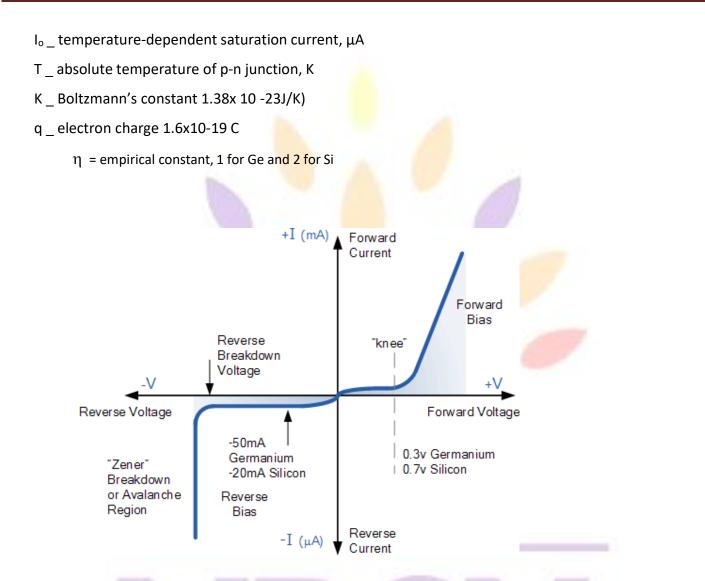

Temperature can have a marked effect on the characteristics of a silicon semiconductor diode as shown in Fig. 11 It has been found experimentally that the reverse saturation current Io will just about double in magnitude for every 10°C increase in temperature.

# your roots to success.

Fig 1.11 Variation in Diode Characteristics with temperature change

It is not uncommon for a germanium diode with an I<sub>o</sub> in the order of 1 or 2 A at 25°C to have a leakage current of 100 A - 0.1 mA at a temperature of 100°C. Typical values of I<sub>o</sub> for silicon are much lower than that of germanium for similar power and current levels. The result is that even at high temperatures the levels of I<sub>o</sub> for silicon diodes do not reach the same high levels obtained. For germanium—a very important reason that silicon devices enjoy a significantly higher level of development and utilization in design. Fundamentally, the open-circuit equivalent in the reverse bias region is better realized at any temperature with silicon than with germanium. The increasing levels of I<sub>o</sub> with temperature account for the lower levels of threshold voltage, as shown in Fig. 1.11. Simply increase the level of I<sub>o</sub> in and not rise in diode current. Of course, the level of TK also will be increase, but the increasing level of I<sub>o</sub> will overpower the smaller percent change in TK. As the temperature increases the forward characteristics are actually becoming more "ideal,"

#### **IDEAL VERSUS PRACTICAL RESISTANCE LEVELS**

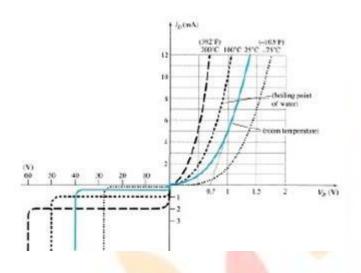

#### **DC or Static Resistance**

The application of a dc voltage to a circuit containing a semiconductor diode will result in an operating point on the characteristic curve that will not change with time. The resistance of the diode at the operating point can be found simply by finding the corresponding levels of VD and ID as shown in Fig. 1.12 and applying the following Equation:

your root

$$R_D = \frac{V_D}{I_D}$$

success...

The dc resistance levels at the knee and below will be greater than the resistance levels obtained for the vertical rise section of the characteristics. The resistance levels in the reverse-bias region will naturally be quite high. Since ohmmeters typically employ a relatively constant-current source, the resistance determined will be at a preset current level (typically, a few mill amperes).

Fig 1.12 Determining the dc resistance of a diode at a particular operating point.

#### AC or Dynamic Resistance

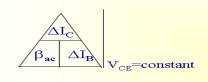

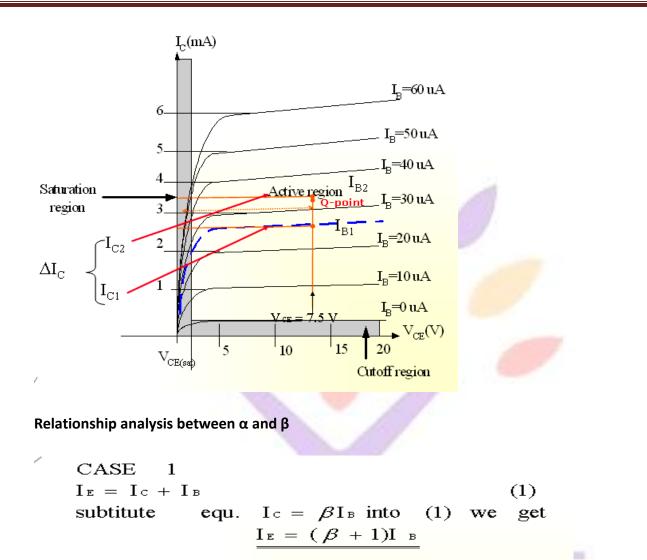

It is obvious from Eq. 1.3 that the dc resistance of a diode is independent of the shape of the characteristic in the region surrounding the point of interest. If a sinusoidal rather than dc input is applied, the situation will change completely. The varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage as shown in Fig. 1.13. With no applied varying signal, the point of operation would be the Q-point appearing on Fig. 1.13 determined by the applied dc levels. The designation Q-point is derived from the word quiescent, which means "still or unvarying." A straight-line drawn tangent to the curve through the Q-point as shown in Fig. 1.13 will define a particular change in voltage and current that can be used to determine the ac or dynamic resistance for this region of the diode characteristics. In equation form,

$$r_d = \frac{\Delta V_d}{\Delta I_d}$$

Where  $\Delta$  Signifies a finite change in the quantity

r roots to success.

Fig 1.13: Determining the ac resistance of a diode at a particular operating point.

#### DIODE EQUIVALENT CIRCUITS

An equivalent circuit is a combination of elements properly chosen to best represent the actual terminal characteristics of a device, system, or such in a particular operating region. In other words, once the equivalent circuit is defined, the device symbol can be removed from a schematic and the equivalent circuit inserted in its place without severely affecting the actual behavior of the system. The result is often a network that can be solved using traditional circuit analysis techniques.

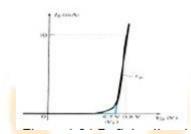

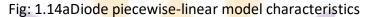

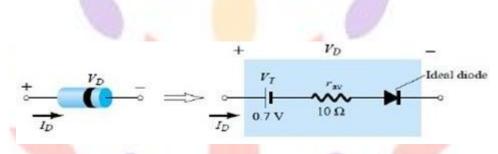

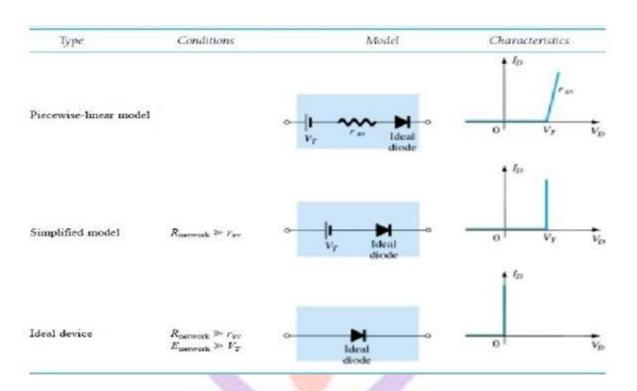

#### Piecewise-Linear Equivalent Circuit

One technique for obtaining an equivalent circuit for a diode is to approximate the characteristics of the device by straight-line segments, as shown in Fig. 1.31. The resulting equivalent circuit is naturally called the piecewise-linear equivalent circuit. It should be obvious from Fig. 1.31 that the straight-line segments do not result in an exact duplication of the actual characteristics, especially in the knee region. However, the resulting segments are sufficiently close to the actual curve to establish an equivalent circuit that will provide an excellent first approximation to the actual behaviour of the device. The ideal diode is included to establish that there is only one direction of conduction through the device, and a reverse-bias condition will result in the open- circuit state for the device. Since a silicon semiconductor, diode does not reach the conduction state until VD reaches 0.7 V with a forward bias (as shown in Fig. 1.14a), a battery  $V_T$  opposing the conduction direction must appear in the equivalent circuit as shown in Fig. 1.14b. The battery simply specifies that the voltage across the device must be greater than the threshold battery voltage before conduction through the device in the direction dictated by the ideal diode can be established. When conduction is established, the resistance of the diode will be the specified value of  $r_{av}$ .

Fig: 1.14b Diode piecewise-linear model equivalent circuit

The approximate level of  $r_{av}$  can usually be determined from a specified operating point on the specification sheet. For instance, for a silicon semiconductor diode, if IF \_ 10 mA (a forward conduction current for the diode) at VD \_ 0.8 V, we know for silicon that a shift of 0.7 V is required before the characteristics rise.

Fig 1.16: Diode equivalent circuits(models)

#### TRANSITION AND DIFFUSION CAPACITANCE

Electronic devices are inherently sensitive to very high frequencies. Most shunt capacitive effects that can be ignored at lower frequencies because the reactance  $XC=1/2\pi fC$  is very large (opencircuit equivalent). This, however, cannot be ignored at very high frequencies. XC will become sufficiently small due to the high value of f to introduce a low-reactance "shorting" path. In the p-n semiconductor diode, there are two capacitive effects to be considered. In the reverse-bias region we have the transition- or depletion region capacitance (CT), while in the forward-bias region we have the diffusion (CD) or storage capacitance. Recall that the basic equation for the capacitance of a parallel-plate capacitor is defined by C= $\epsilon$ A/d, where  $\epsilon$  is the permittivity of the dielectric (insulator) between the plates of area A separated by a distance d. In the reverse-, bias region there is a depletion region (free of carriers) that behaves essentially like an insulator between the layers of opposite charge. Since the depletion width (d) will increase with increased reverse-bias potential, the resulting transition capacitance will decrease. The fact that the capacitance is dependent on the applied reverse-bias potential has application in a number of electronic systems. Although the effect described above will also be present in the forward-bias region, it is over shadowed by a capacitance effect directly

dependent on the rate at which charge is injected into the regions just outside the depletion region. The capacitive effects described above are represented by a capacitor in parallel with the ideal diode, as shown in Fig. 1.38. For low- or mid-frequency applications (except in the power area), however, the capacitor is normally not included in the diode symbol.

Fig 1.17: Including the effect of the transition or diffusion capacitance on the semiconductor diode

**Diode capacitances:** The diode exhibits two types of capacitances transition capacitance and diffusion capacitance.

- Transition capacitance: The capacitance which appears between positive ion layer in n-region and negative ion layer in p-region.

- Diffusion capacitance: This capacitance originates due to diffusion of charge carriers in the opposite regions.

The transition capacitance is very small as compared to the diffusion capacitance.

In reverse bias transition, the capacitance is the dominant and is given by:

$$C_T = \varepsilon A/W$$

where C<sub>T</sub> - transition capacitance

A - diode cross sectional area

W - depletion region width

In forward bias, the diffusion capacitance is the dominant and is given by:

$C_D = dQ/dV = \tau^* dI/dV = \tau^* g = \tau/r$  (general)

where  $C_D$  - diffusion capacitance

dQ - change in charge stored in depletion region

V - change in applied voltage

- $\tau$  time interval for change in voltage

- g diode conductance

- r diode resistance

CSE,NRCM

K.ANNAMMA, Assistant Professor

success.

The diffusion capacitance at low frequencies is given by the formula:

$C_D = \tau^* g/2$  (low frequency)

The diffusion capacitance at high frequencies is inversely proportional to the frequency and is given by the formula:

$C_{D}=g(\tau/2\omega)^{\,{}^{t/_{2}}}$

*Note: The variation of diffusion capacitance with applied voltage is used in the design of varactor.*

#### **BREAK DOWN MECHANISMS**

When an ordinary <u>P-N junction diode</u> is reverse biased, normally only very small reverse saturation current flows. This current is due to movement of minority carriers. It is almost independent of the voltage applied. However, if the reverse bias is increased, a point is reached when the junction breaks down and the reverse current increases abruptly. This current could be large enough to destroy the junction. If the reverse current is limited by means of a suitable series resistor, the power dissipation at the junction will not be excessive, and the device may be operated continuously in its breakdown region to its normal (reverse saturation) level. It is found that for a suitably designed diode, the breakdown voltage is very stable over a wide range of reverse currents. This quality gives the breakdown diode many useful applications as a voltage reference source.

The critical value of the voltage, at which the breakdown of a P-N junction diode occurs, is called the *breakdown voltage*. The breakdown voltage depends on the width of the depletion region, which, in turn, depends on the doping level. The junction offers almost zero resistance at the breakdown point.

There are two mechanisms by which breakdown can occur at a reverse biased P-N junction:

- 1. avalanche breakdown and

- 2. Zener breakdown.

#### Avalanche breakdown

The minority carriers, under reverse biased conditions, flowing through the junction acquire a kinetic energy which increases with the increase in reverse voltage. At a sufficiently high reverse voltage (say 5 V or more), the kinetic energy of minority carriers becomes so large that they knock out electrons from the covalent bonds of the semiconductor material. As a result of collision, the liberated electrons in turn liberate more electrons and the current becomes very large leading to the breakdown

of the crystal structure itself. This phenomenon is called the avalanche breakdown. The breakdown region is the knee of the characteristic curve. Now the current is not controlled by the junction voltage but rather by the external circuit.

#### Zener breakdown

Under a very high reverse voltage, the depletion region expands and the potential barrier increases leading to a very high electric field across the junction. The electric field will break some of the covalent bonds of the semiconductor atoms leading to a large number of free minority carriers, which suddenly increase the reverse current. This is called the Zener effect. The breakdown occurs at a particular and constant value of reverse voltage called the breakdown voltage, it is found that Zener breakdown occurs at electric field intensity of about  $3 \times 10^7$  V/m.

Fig 1.18: Diode characteristics with breakdown

Either of the two (Zener breakdown or avalanche breakdown) may occur independently, or both of these may occur simultaneously. Diode junctions that breakdown below 5 V are caused by Zener effect. Junctions that experience breakdown above 5 V are caused by avalanche effect. Junctions that breakdown around 5 V are usually caused by combination of two effects. The Zener breakdown occurs in heavily doped junctions (P-type semiconductor moderately doped and N-type heavily doped), which produce narrow depletion layers. The avalanche breakdown occurs in lightly doped junctions, which produce wide depletion layers. With the increase in junction temperature Zener breakdown voltage is reduced while the avalanche breakdown voltage increases. The Zener diodes have a negative temperature coefficient while avalanche diodes have a positive temperature coefficient. Diodes that have breakdown voltages around 5 V have zero temperature coefficient. The breakdown phenomenon is reversible and harmless so long as the safe operating temperature is maintained.

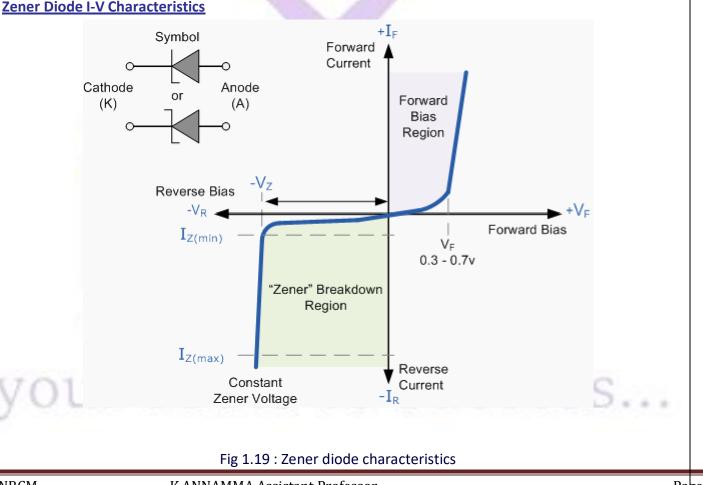

#### **ZENER DIODES**

The **Zener diode** is like a general-purpose signal diode consisting of a silicon PN junction. When biased in the forward direction it behaves just like a normal signal diode passing the rated current, but as soon as a reverse voltage applied across the zener diode exceeds the rated voltage of the device, the diodes breakdown voltage  $V_B$  is reached at which point a process called *Avalanche Breakdown* occurs in the semiconductor depletion layer and a current starts to flow through the diode to limit this increase in voltage.

The current now flowing through the zener diode increases dramatically to the maximum circuit value (which is usually limited by a series resistor) and once achieved this reverse saturation current remains fairly constant over a wide range of applied voltages. This breakdown voltage point, V<sub>B</sub> is called the "zener voltage" for zener diodes and can range from less than one volt to hundreds of volts.

The point at which the zener voltage triggers the current to flow through the diode can be very accurately controlled (to less than 1% tolerance) in the doping stage of the diodes semiconductor construction giving the diode a specific *zener breakdown voltage*, (Vz) for example, 4.3V or 7.5V. This zener breakdown voltage on the I-V curve is almost a vertical straight line.

The **Zener Diode** is used in its "reverse bias" or reverse breakdown mode, i.e. the diodes anode connects to the negative supply. From the I-V characteristics curve above, we can see that the zener diode has a region in its reverse bias characteristics of almost a constant negative voltage regardless of the value of the current flowing through the diode and remains nearly constant even with large changes in current as long as the zener diodes current remains between the breakdown current  $I_{Z(min)}$  and the maximum current rating  $I_{Z(max)}$ .

This ability to control itself can be used to great effect to regulate or stabilize a voltage source against supply or load variations. The fact that the voltage across the diode in the breakdown region is almost constant turns out to be an important application of the zener diode as a voltage regulator. The function of a regulator is to provide a constant output voltage to a load connected in parallel with it in spite of the ripples in the supply voltage or the variation in the load current and the zener diode will continue to regulate the voltage until the diodes current falls below the minimum  $I_{Z(min)}$  value in the reverse breakdown region.

# SPECIAL PURPOSE ELECTRONIC DEVICES

#### PRINCIPLE OF OPERATION AND CHARACTERISTICS OF TUNNEL DIODE

A **tunnel diode** or **Esaki diode** is a type of semiconductor diode which is capable of very fast operation, well into the microwave frequency region, by using quantum mechanical effects.

It was invented in August 1957 by Leo Esaki when he was with Tokyo Tsushin Kogyo, now known as Sony. In 1973 he received the Nobel Prize in Physics, jointly with Brian Josephson, for discovering the electron tunneling effect used in these diodes. Robert Noyce independently came up with the idea of a tunnel diode while working for William Shockley, but was discouraged from pursuing it.

Fig 1.19: Tunnel diode schematic symbol

These diodes have a heavily doped p–n junction only some 10 nm (100 Å) wide. The heavy doping results in a broken bandgap, where conduction band electron states on the n-side are more or less aligned with valence band hole states on the p-side. Tunnel diodes were manufactured by Sony for the first time in 1957 followed by General Electric and other companies from about 1960, and are still made in low volume today. Tunnel diodes are usually made from germanium, but can also be made in gallium arsenide and silicon materials. They can be used as oscillators, amplifiers, frequency converters and detectors.Tunnelling Phenomenon:

In a conventional semiconductor diode, conduction takes place while the p-n junction is forward biased and blocks current flow when the junction is reverse biased. This occurs up to a point known as the "reverse breakdown voltage" when conduction begins (often accompanied by destruction of the device). In the tunnel diode, the dopant concentration in the p and n layers are increased to the point where the **reverse breakdown voltage** becomes **zero** and the diode conducts in the reverse direction. However, when forward-biased, an odd effect occurs called "quantum mechanical tunnelling" which gives rise to a region where an *increase* in forward voltage is accompanied by a *decrease* in forward current. This negative resistance region can be exploited in a solid state version of the dynatron oscillator which normally uses a tetrode thermionic valve (or tube).

#### Forward bias operation

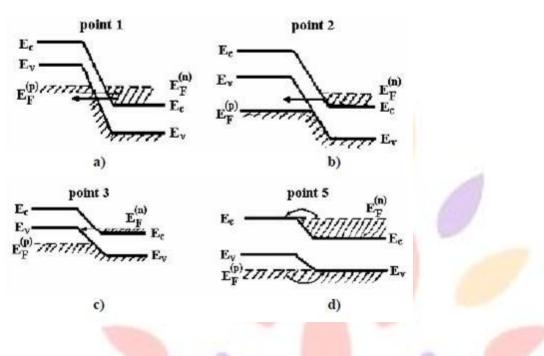

Under normal forward bias operation, as voltage begins to increase, electrons at first tunnel through the very narrow p–n junction barrier because filled electron states in the conduction band on the nside become aligned with empty valence band hole states on the p-side of the p-n junction. As voltage increases further these states become more misaligned and the current drops – this is called *negative resistance* because current decreases with increasing voltage. As voltage increases yet further, the diode begins to operate as a normal diode, where electrons travel by conduction across the p–n junction, and no longer by tunneling through the p–n junction barrier. Thus the most importantoperating region for a tunnel diode is the negative resistance region.

#### **Reverse bias operation**

When used in the reverse direction they are called **back diodes** and can act as fast rectifiers with zero offset voltage and extreme linearity for power signals (they have an accurate square law characteristic in the reverse direction).

Under reverse bias filled states on the p-side become increasingly aligned with empty states on the nside and electrons now tunnel through the pn junction barrier in reverse direction – this is the Zener effect that also occurs in zener diodes.

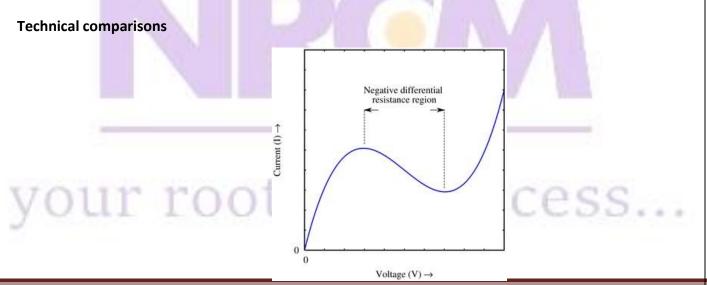

#### Fig 1.20a: current-voltage characteristic of tunnel diode

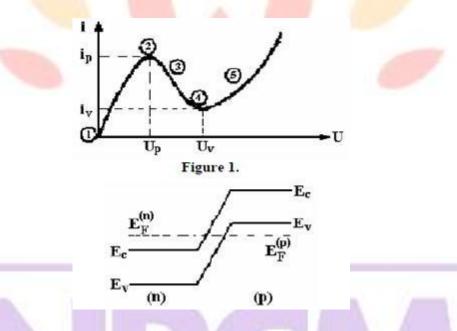

A rough approximation of the VI curve for a tunnel diode, showing the negative differential resistance region. The Japanese physicist Leo Esaki invented the tunnel diode in 1958. It consists of a p-n junction with highly doped regions. Because of the thinness of the junction, the electrons can pass through the potential barrier of the dam layer at a suitable polarization, reaching the energy states on the other sides of the junction. The current-voltage characteristic of the diode is represented in Figure 1.20a. In this sketch *i p* and *Up* are the peak, and *iv* and *Uv* are the valley values for the current and voltage respectively. The form of this dependence can be qualitatively explained by considering the tunneling processes that take place in a thin p-n junction.

#### Energy band structure of tunnel diode:

Fig 1.20b Energy band structure of tunnel diode

For the degenerated semiconductors, the energy band diagram at thermal equilibrium is presented in Figure 1.20b.

In Figure 1.20c the tunneling processes in different points of the current voltage characteristic for the tunnel diode are presented.

# your roots to success..

Advantages of tunnel diodes:

- Environmental immunity i.e. peak point is not a function of temperature.

- Low cost.

- Low noise.

- Low power consumption.

- High speed i.e. tunneling takes place very fast at the speed of light in the order of nanoseconds

- Simplicity i.e. a tunnel diode can be used along with a d.c supply and a few passive elements to obtain various application circuits.

#### **Applications for tunnel diodes:**

- local oscillators for UHF television tuners

- Trigger circuits in oscilloscopes

- High speed counter circuits and very fast-rise time pulse generator circuits

- The tunnel diode can also be used as low-noise microwave amplifier.

## VARACTOR DIODE

Varactor diode is a special type of diode which uses transition capacitance property i.e voltage variable capacitance .These are also called as varicap,VVC(voltage variable capacitance) or tuning diodes.

The varactor diode symbol is shown below with a diagram representation.

CSE,NRCM

MMA, Assistant Professor

Page 29

Fig 1.21a:symbol of varactor diode

When a reverse voltage is applied to a PN junction, the holes in the p-region are attracted to the anode terminal and electrons in the n-region are attracted to the cathode terminal creating a region where there is little current. This region ,the depletion region, is essentially devoid of carriers and behaves as the dielectric of a capacitor.

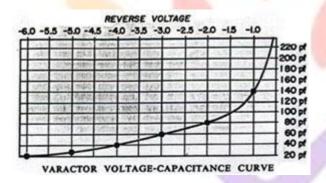

The depletion region increases as reverse voltage across it increases; and since capacitance varies inversely as dielectric thickness, the junction capacitance will decrease as the voltage across the PN junction increases. So by varying the reverse voltage across a PN junction the junction capacitance can be varied .This is shown in the typical varactor voltage-capacitance curve below.

Notice the nonlinear increase in capacitance as the reverse voltage is decreased. This nonlinearity allows the varactor to be used also as a harmonic generator.

Major varactor considerations are: (a) Capacitance value (b) Voltage (c) Variation in capacitance with voltage. (d) Maximum working voltage (e) Leakage current **Applications:** Tuned circuits. FM modulators Automatic frequency control devices Adjustable bandpass filters o success. Parametric amplifiers Television receivers. **PRINCIPLE OF OPERATION OF SCR** CSE,NRCM K.ANNAMMA, Assistant Professor

Page 30

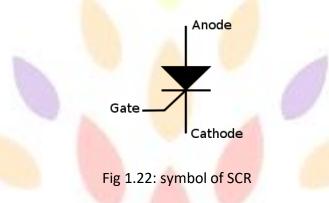

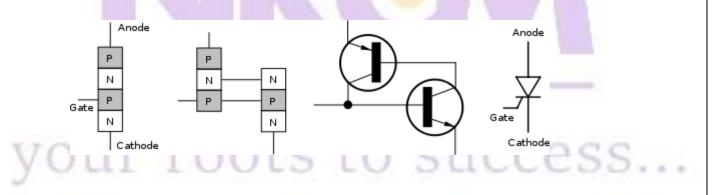

A **silicon-controlled rectifier** (or **semiconductor-controlled rectifier**) is a four-layer solid state device that controls current. The name "silicon controlled rectifier" or **SCR** is General Electric's trade name for a type of thyristor. The SCR was developed by a team of power engineers led by Gordon Hall and commercialized by Frank W. "Bill" Gutzwiller in 1957.symbol of SCR is given below:

#### **Construction of SCR**

An SCR consists of four layers of alternating P and N type semiconductor materials. Silicon is used as the intrinsic semiconductor, to which the proper dopants are added. The junctions are either diffused or alloyed. The planar construction is used for low power SCRs (and all the junctions are diffused). The mesa type construction is used for high power SCRs. In this case, junction J2 is obtained by the diffusion method and then the outer two layers are alloyed to it, since the PNPN pellet is required to handle large currents. It is properly braced with tungsten or molybdenum plates to provide greater mechanical strength. One of these plates is hard soldered to a copper stud, which is threaded for attachment of heat sink. The doping of PNPN will depend on the application of SCR, since its characteristics are similar to those of the thyratron. Today, the term thyristor applies to the larger family of multilayer devices that exhibit bistable state-change behaviour, that is, switching either ON or OFF.

The operation of a SCR and other thyristors can be understood in terms of a pair of tightly coupled bipolar junction transistors, arranged to cause the self-latching action. The following figures are construction of SCR, its two transistor model and symbol respectively

Fig 1.23: Construction, Two transistor model of SCR and symbol of SCR SCR Working Principle

Fig 1.24: Current flow and voltage bias in an SCR

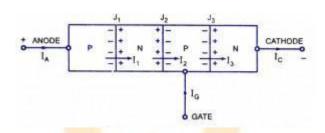

The **SCR** is a four-layer, three-junction and a three-terminal device and is shown in fig.1.24. The end Pregion is the anode, the end N-region is the cathode and the inner P-region is the gate. The anode to cathode is connected in series with the load circuit. Essentially the device is a switch. Ideally it remains off (voltage blocking state), or appears to have an infinite impedance until both the anode and gate terminals have suitable positive voltages with respect to the cathode terminal. The thyristor then switches on and current flows and continues to conduct without further gate signals. Ideally the thyristor has zero impedance in conduction state. For switching off or reverting to the blocking state, there must be no gate signal and the anode current must be reduced to zero. Current can flow only in one direction.

In absence of external bias voltages, the majority carrier in each layer diffuses until there is a built-in voltage that retards further diffusion. Some majority carriers have enough energy to cross the barrier caused by the retarding electric field at each junction. These carriers then become minority carriers and can recombine with majority carriers. Minority carriers in each layer can be accelerated across each junction by the fixed field, but because of absence of external circuit in this case the sum of majority and minority carrier currents must be zero.

A voltage bias, as shown in figure, and an external circuit to carry current allow internal currents which include the following terms:

The current I<sub>x</sub> is due to

- Majority carriers (holes) crossing junction J<sub>1</sub>

- Minority carriers crossing junction J<sub>1</sub>

- Holes injected at junction  $J_2$  diffusing through the N-region and crossing junction  $J_1$  and

- Minority carriers from junction J<sub>2</sub> diffusing through the N-region and crossing junction J<sub>1</sub>.

# your roots to success.

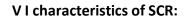

Fig 1.25: V-I characteristics of SCR

As already mentioned, the SCR is a four-layer device with three terminals, namely, the anode, the cathode and the gate. When the anode is made positive with respect to the cathode, junctions  $J_1$  and  $J_3$ are forward biased and junction J<sub>2</sub> is reverse-biased and only the leakage current will flow through the device. The SCR is then said to be in the forward blocking state or in the forward mode or off state. But when the cathode is made positive with respect to the anode, junctions  $J_1$  and  $J_3$  are reverse-biased, a small reverse leakage current will flow through the SCR and the SGR is said to be in the reverse blocking state or in reverse mode.

When the anode is positive with respect to cathode i.e. when the SCR is in forward mode, the SCR does not conduct unless the forward voltage exceeds certain value, called the forward breakover voltage, VFBO. In non-conducting state, the current through the SCR is the leakage current which is very small and is negligible. If a positive gate current is supplied, the SCR can become conducting at a voltage much lesser than forward break-over voltage. The larger the gate current, lower the break-over voltage. With sufficiently large gate current, the SCR behaves identical to PN rectifier. Once the SCR is switched on, the forward voltage drop across it is suddenly reduced to very small value, say about 1

volt. In the conducting or on-state, the current through the SCR is limited by the external impedance.

When the anode is negative with respect to cathode, that is when the SCR is in reverse mode or in blocking state no current flows through the SCR except very small leakage current of the order of few micro-amperes. But if the reverse voltage is increased beyond a certain value, called the reverse break-over voltage,  $V_{RB0}$  avalanche break down takes place. Forward break-over voltage  $V_{FB0}$  is usually higher than reverse breakover voltage,  $V_{RB0}$ .

From the foregoing discussion, it can be seen that the SCR has two stable and reversible operating states. The change over from off-state to on-state, called turn-on, can be achieved by increasing the forward voltage beyond  $V_{FBO}$ . A more convenient and useful method of turn-on the device employs the gate drive. If the forward voltage is less than the forward break-over voltage,  $V_{FBO}$ , it can be turned-on by applying a positive voltage between the gate and the cathode. This method is called the gate control. Another very important feature of the gate is that once the SCR is triggered to on-state the gate loses its control.

#### The switching action of gate takes place only when

(i) SCR is forward biased i.e. anode is positive with respect to cathode, and

(ii) Suitable positive voltage is applied between the gate and the cathode.

Once the SCR has been switched on, it has no control on the amount of current flowing through it. The current through the SCR is entirely controlled by the external impedance connected in the circuit and the applied voltage. There is, however, a very small, about 1 V, potential drop across the SCR. The forward current through the SCR can be reduced by reducing the applied voltage or by increasing the circuit impedance. There is, however, a minimum forward current that must be maintained to keep the SCR in conducting state. This is called the holding current rating of SCR. If the current through the SCR is reduced below the level of holding current, the device returns to off-state or blocking state.

The SCR can be switched off by reducing the forward current below the level of holding current which may be done either by reducing the applied voltage or by increasing the circuit impedance.

Note : The gate can only trigger or switch-on the SCR, it cannot switch off.

Alternatively the SCR can be switched off by applying negative voltage to the anode (reverse mode), the SCR naturally will be switched off.

Here one point is worth mentioning, the SCR takes certain time to switch off. The time, called the turnoff time, must be allowed before forward voltage may be applied again otherwise the device will switch-on with forward voltage without any gate pulse. The turn-off time is about 15 micro-seconds, which is immaterial when dealing with power frequency, but this becomes important in the inverter circuits, which are to operate at high frequency.

#### **Merits of SCR**

- 1. Very small amount of gate drive is required.

- 2.SCRs with high voltage and current ratings are available.

- 3.On state losses of SCR are less.

#### **Demerits of SCR**

- 1.Gate has no control, once SCR is turned on.

- 2.External circuits are required for turning it off.

- 3. Operationg frequencies are low.

- 4.Additional protection circuits are required.

#### **Application of SCRs**

SCRs are mainly used in devices where the control of high power, possibly coupled with high voltage, is demanded. Their operation makes them suitable for use in medium to high-voltage AC power control applications, such as lamp dimming, regulators and motor control.

SCRs and similar devices are used for rectification of high power AC in high-voltage direct current power transmission

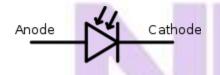

#### **PHOTO DIODE**

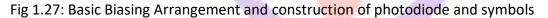

The photo diode is a semiconductor p-n junction device whose region of operation is limited to the reverse biased region. The figure below shows the symbol of photodiode

Fig 1.26:Symbol of photodiode.

#### Principle of operation:

A photodiode is a type of photo detector capable of converting light into either current or voltage, depending upon the mode of operation. The common, traditional solar cell used to generate electric solar power is a large area photodiode. A photodiode is designed to operate in reverse bias. The deletion region width is large. Under normal conditions it carries small reverse current due to minority charge carriers. When light is incident through glass window on the p-n junction, photons in the light

bombard the p-n junction and some energy s imparted to the valence electrons. So valence electrons break covalent bonds and become free electrons. Thus more electron-hole pairs are generated. Thus total number of minority charge carriers increases and hence reverse current increases. This is the basic principle of operation of photo diode.

#### **Characteristics of photodiode:**

When the P-N junction is reverse-biased, a reverse saturation current flows due to thermally generated holes and electrons being swept across the junction as the minority carriers. With the increase in temperature of the junction more and more hole-electron pairs are created and so the reverse saturation current  $I_0$  increases. The same effect can be had by illuminating the junction. When light energy bombards a P-N junction, it dislodges valence electrons. The more light striking the junction the larger the reverse current in a diode. It is due to generation of more and more charge carriers with the increase in level of illumination. This is clearly shown in ' figure for different intensity levels. The dark current is the current that exists when no light is incident. It is to be noted here that current becomes zero only with a positive applied bias equals to  $V_0$ . The almost equal spacing between the curves for the same increment in luminous flux reveals that the reverse saturation current  $I_0$  increases linearly with the luminous flux as shown in figure. Increase in reverse voltage does not increase the reverse current significantly, because all available charge carriers are already being swept across the junction. For reducing the reverse saturation current  $I_0$  to zero, it is necessary to forward bias the junction by an amount equal to barrier potential. Thus the photodiode can be used as a photoconductive device.

# your roots to success..

Fig 1.28: characteristics of photodiode

On removal of reverse bias applied across the photodiode, minority charge carriers continue to be swept across the junction while the diode is illuminated. This has the effect of increasing the concentration of holes in the P-side and that of electrons in the N-side But the barrier potential is negative on the P-side and positive on the N-side, and was created by holes flowing from P to N-side and electrons from N to P-side during fabrication of junction. Thus the flow of minority carriers tends to reduce the barrier potential.

When an external circuit is connected across the diode terminals, the minority carrier; return to the original side via the external circuit. The electrons which crossed the junction from P to N-side now flow out through the N-terminal and into the P-terminal This means that the device is behaving as a voltage cell with the N-side being the negative terminal and the P-side the positive terminal. Thus, the photodiode is & photovoltaic device as well as photoconductive device.

# Advantages: The advantages of photodiode are: 1.It can be used as variable resistance device. 2.Highly sensitive to the light. 3.The speed of operation is very high. Disadvantages: 1.Temperature dependent dark current. 2.poor temperature stability. 3.Current needs amplification for driving other circuits. Applications: 1.Alarm system. 2.counting system.

K.ANNAMMA, Assistant Professor

# **UNIT II RECTIFIERS & FILTERS**

#### **INTRODUCTION**

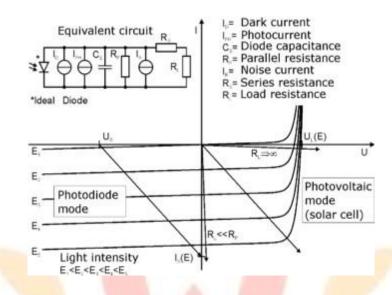

For the operation of most of the electronics devices and circuits, a d.c. source is required. So it is advantageous to convert domestic a.c. supply into d.c.voltages. The process of converting a.c. voltage into d.c. voltage is called as rectification. This is achieved with i) Step-down Transformer, ii) Rectifier, iii) Filter and iv) Voltage regulator circuits.

These elements constitute d.c. regulated power supply shown in the fig 1 below.

Fig 2.1: Block Diagram of regulated D.C Power Supply

- ✓ Transformer steps down 230V AC mains to low voltage AC.

- ✓ Rectifier converts AC to DC, but the DC output is varying.

- ✓ Smoothing smooth the DC from varying greatly to a small ripple.

- ✓ Regulator eliminates ripple by setting DC output to a fixed voltage.

The block diagram of a regulated D.C. power supply consists of step-down transformer, rectifier, filter, voltage regulator and load. An ideal regulated power supply is an electronics circuit designed to provide a predetermined d.c. voltage Vo which is independent of the load current and variations in the input voltage ad temperature. If the output of a regulator circuit is a AC voltage then it is termed as voltage stabilizer, whereas if the output is a DC voltage then it is termed as voltage regulator.

#### RECTIFIER

Any electrical device which offers a low resistance to the current in one direction but a high resistance to the current in the opposite direction is called rectifier. Such a device is capable of converting a sinusoidal input waveform, whose average value is zero, into a unidirectional Waveform, with a nonzero average component. A rectifier is a device, which converts a.c. voltage (bi-directional) to pulsating

d.c. voltage (Unidirectional).

#### **Characteristics of a Rectifier Circuit:**

Any electrical device which offers a low resistance to the current in one direction but a high resistance to the current in the opposite direction is called rectifier. Such a device is capable of converting a sinusoidal input waveform, whose average value is zero, into a unidirectional waveform, with a nonzero average component.

A rectifier is a device, which converts a.c. voltage (bi-directional) to pulsating d.c..Load currents: They are two types of output current. They are average or d.c. current and RMS currents.

Average or DC current: The average current of a periodic function is defined as the area of one cycle of the curve divided by the base.

It is expressed mathematically as

i) Average value/dc value/mean value=  $\frac{Area \ over \ one \ period}{Total \ time \ period}$

$$V_{dc} = \frac{1}{T} \int_{0}^{T} V d(wt)$$

ii) Effective (or) R.M.S current:

The effective (or) R.M.S. current squared of a periodic function of time is given by the area of one cycle of the curve, which represents the square of the function divided by the base.

$$V_{rms} = \sqrt{\frac{1}{T} \int_{0}^{T} V^2 d(wt)}$$

iii) Peak factor:

It is the ratio of peak value to Rms value

Peak factor =  $\frac{peakvalue}{rmsvalue}$

cess.

iv) Form factor:

It is the ratio of Rms value to average value

#### v) Ripple Factor ( $\Gamma$ ) :

It is defined as ration of R.M.S. value of a.c. component to the d.c. component in the output is known as "Ripple Factor".

$$\Gamma = \frac{V_{ac}}{V_{dc}}$$

$$V_{ac} = \sqrt{V_{rms}^2 - V_{dc}^2}$$

vi) Efficiency ( $\eta$ ):

It is the ratio of d.c output power to the a.c. input power. It signifies, how efficiently the rectifier circuit

#### converts a.c. power into d.c. power.

$$\eta = \frac{o / p \text{ power}}{i / p \text{ power}}$$

vii) Peak Inverse Voltage (PIV):

It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction.

viii) Transformer Utilization Factor (UTF):

The d.c. power to be delivered to the load in a rectifier circuit decides the rating of the

Transformer used in the circuit. So, transformer utilization factor is defined as

$$TUF = \frac{P_{dc}}{P_{ac(rated)}}$$

ix) % Regulation:

The variation of the d.c. output voltage as a function of d.c. load current is called regulation. The percentage regulation is defined as

% Re gulation =

$$\frac{V_{NL} - V_{FL}}{V_{FL}} * 100$$

For an ideal power supply, % Regulation is zero.

#### **CLASSIFICATION OF RECTIFIERS**

Using one or more diodes in the circuit, following rectifier circuits can be designed.

- 1) Half Wave Rectifier

- 2) Full Wave Rectifier

- 3) Bridge Rectifier

#### HALF-WAVE RECTIFIER:

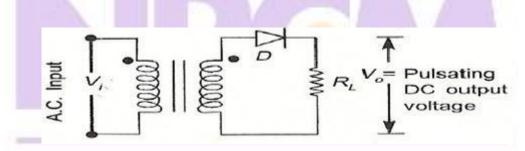

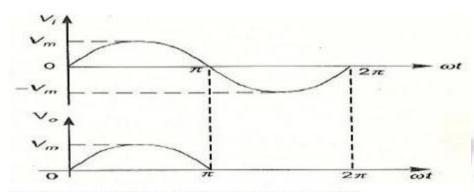

A Half – wave rectifier as shown in **fig 1.2** is one, which converts a.c. voltage into a pulsating voltage using only one half cycle of the applied a.c. voltage.

Fig 1.2: Basic structure of Half-Wave Rectifier

The a.c. voltage is applied to the rectifier circuit using step-down transformer-rectifying element i.e., pn junction diode and the source of a.c. voltage, all connected is series. The a.c. voltage is applied to the rectifier circuit using step-down transformer

fig 3 Input and output waveforms of a Half wave rectifier

V=V<sub>m</sub>sin (wt)

The input to the rectifier circuit, Where  $V_m$  is the peak value of secondary a.c. voltage.

#### **Operation:**

For the positive half-cycle of input a.c. voltage, the diode D is forward biased and hence it conducts. Now a current flows in the circuit and there is a voltage drop across RL. The waveform of the diode current (or) load current is shown in **fig 3**.

For the negative half-cycle of input, the diode D is reverse biased and hence it does not Conduct. Now no current flows in the circuit i.e., i=0 and Vo=0. Thus for the negative half- cycle no power is delivered to the load.

ts to success.

#### Analysis:

In the analysis of a HWR, the following parameters are to be analyzed.

- 1. DC output current

- 2. DC Output voltage

- 3. R.M.S. Current

- 4. R.M.S. voltage

- 5. Rectifier Efficiency ( $\eta$ )

- 6. Ripple factor (γ)

- 7. Peak Factor

- 8. % Regulation

- 9. Transformer Utilization Factor (TUF)

- 10. form factor

- 11. o/p frequency

Let a sinusoidal voltage Vi be applied to the input of the rectifier.

Then  $V=V_m \sin (wt)$  Where  $V_m$  is the maximum value of the secondary voltage. Let the diode be idealized to piece-wise linear approximation with resistance Rf in the forward direction i.e., in the ON state and Rr (= $\infty$ ) in the reverse direction i.e., in the OFF state. Now the current 'i' in the diode (or) in the load resistance RL is given by  $V=V_m \sin (wt)$

#### i) AVERAGE VOLTAGE

$$V_{dc} = \frac{1}{T} \int_{0}^{T} V d(wt)$$

$$V_{dc} = \frac{1}{T} \int_{0}^{2\Pi} V(\alpha) d\alpha$$

$$V_{dc} = \frac{1}{2\Pi} \int_{\Pi}^{2\Pi} V(\alpha) d\alpha$$

$$V_{dc} = \frac{1}{2\Pi} \int_{0}^{V} V_m \sin(wt)$$

$$V_{dc} = \frac{V_m}{\Pi}$$

ts to success...

#### ii).AVERAGE CURRENT:

Π

#### iii) RMS VOLTAGE:

The value of TUF is low which shows that in half-wave circuit, the transformer is not fully utilized.

If the transformer rating is 1 KVA (1000VA) then the half-wave rectifier can deliver

1000 X 0.287 = 287 watts to resistance load.

Peak Inverse Voltage (PIV):

It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction. The peak inverse voltage across a diode is the peak of the negative half- cycle. For half-wave rectifier, PIV is Vm.

#### DISADVANTAGES OF HALF-WAVE RECTIFIER:

- 1. The ripple factor is high.

- 2. The efficiency is low.

- 3. The Transformer Utilization factor is low.

Because of all these disadvantages, the half-wave rectifier circuit is normally not used as a power rectifier circuit.

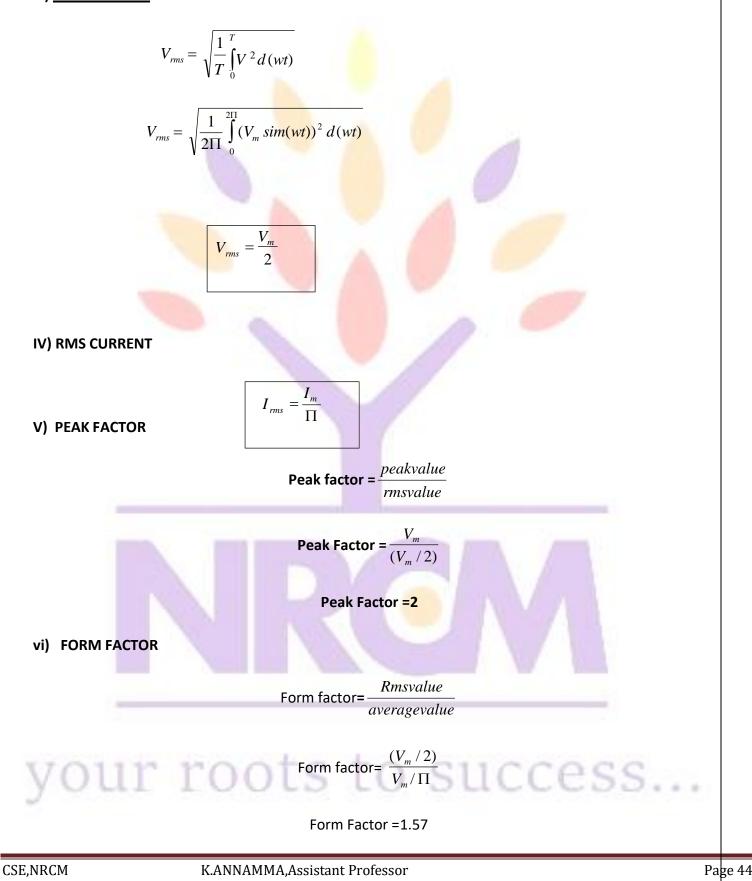

#### FULL WAVE RECTIFIER:

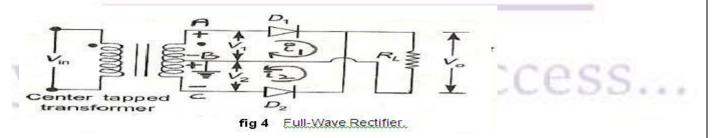

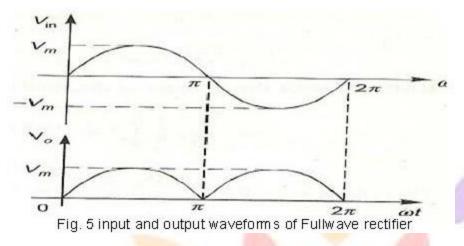

A full-wave rectifier converts an ac voltage into a pulsating dc voltage using both half cycles of the applied ac voltage. In order to rectify both the half cycles of ac input, two diodes are used in this circuit. The diodes feed a common load RL with the help of a center-tap transformer. A center-tap transformer is the one, which produces two sinusoidal waveforms of same magnitude and frequency but out of phase with respect to the ground in the secondary winding of the transformer. The full wave rectifier is shown in the **fig 4** below

K.ANNAMMA, Assistant Professor

Page 46

Fig. 5 shows the input and output wave forms of the ckt.

During positive half of the input signal, anode of diode D1 becomes positive and at the same time the anode of diode D2 becomes negative. Hence D1 conducts and D2 does not conduct. The load current flows through D1 and the voltage drop across RL will be equal to the input voltage.

During the negative half cycle of the input, the anode of D1 becomes negative and the anode of D2 becomes positive. Hence, D1 does not conduct and D2 conducts. The load current flows through D2 and the voltage drop across RL will be equal to the input voltage. It is noted that the load current flows in the both the half cycles of ac voltage and in the same direction through the load resistance.

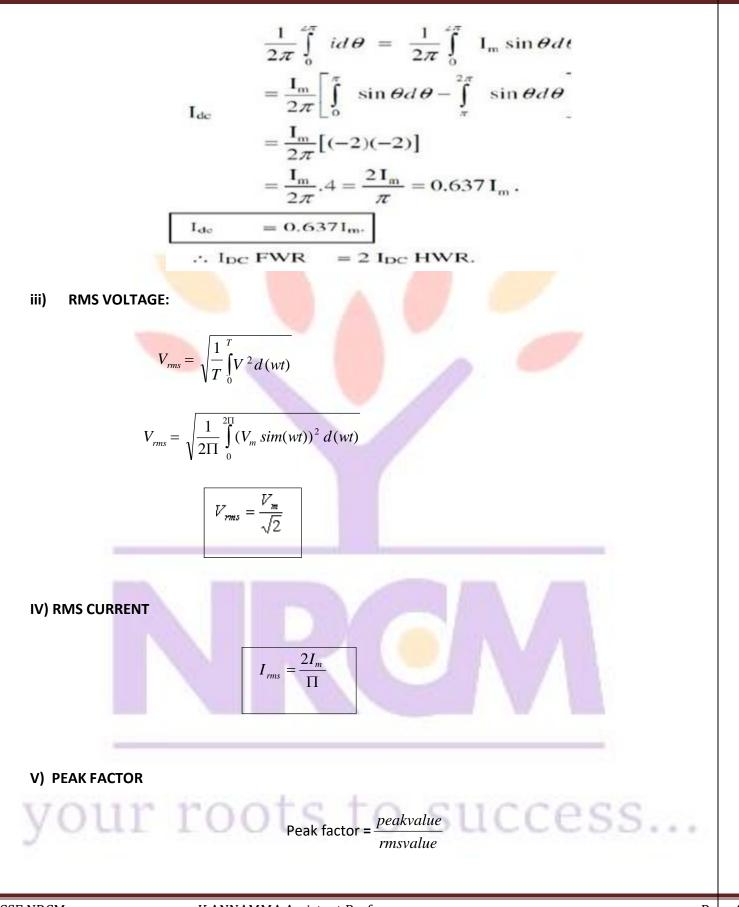

i) AVERAGEVOLTAGE

$$V_{dc} = I_{dc} \cdot R_L \cdot = \frac{2 \, \mathbf{I}_m}{\pi} \cdot R_L \quad \text{We know } \mathbf{I}_m = \frac{V_m}{R_s + R_f + R_L}$$

$$\therefore V_{dc} = \frac{2 \cdot V_m R_L}{\pi (R_s + R_f + R_L)}$$

$$If(R_s + R_f) << R_L$$

$$V_{dc} = \frac{2V_m}{\pi} = 0.637 V_m.$$

# ii) \_AVERAGE CURRENT

CSE,NRCM

K.ANNAMMA, Assistant Professor

Page 48

Peak Factor =  $\frac{V_m}{(V_m/2)}$

Peak Factor =2

vi) FORM FACTOR

Form factor=  $\frac{(V_m / \sqrt{2})}{2V_m / \Pi}$

Form Factor =1.11

vii) Ripple Factor:

$$\gamma = \sqrt{\left(\frac{I_{rms}}{I_{dc}}\right)^{2} - 1}$$

for FWR,

$$I_{rms} = \frac{I_{m}}{\sqrt{2}} \ll I_{DC} = \frac{2I_{m}}{\pi}$$

$$\therefore \gamma_{FWR} = \sqrt{\left(\frac{I_{m}}{\sqrt{2}} / \frac{2I_{m}}{\pi}\right)^{2} - 1}$$

$$= \sqrt{\left(\frac{\pi}{2\sqrt{2}}\right)^{2} - 1}$$

$$= \sqrt{\left(\frac{3.1416}{2 \times 1.414}\right)^{2} - 1} = 0.483$$

viii) Efficiency ( $\eta$ ):

$$\eta = \frac{o/ppower}{i/ppower} *100$$

YOUT TOOTS to success...

$$\eta = \frac{p_{dc}}{p_{ac}} \times 100\%$$

For FWR,  $p_{dc} = I_{dc}^2 \cdot R_L = \left(\frac{2}{\pi} \cdot I_m\right)^2 \cdot R_L$

$$P_{ac} = I^2 r_{ms} (R_f + R_S + R_L)$$

$$\left(\frac{I_m}{\sqrt{2}}\right)^2 (R_f + R_s + R_L)$$

$$\eta = \frac{\frac{I^2 \cdot m^4}{\pi^2} \cdot R_L}{\frac{I^2 \cdot m^2}{2} \cdot (R_f + R_s + R_L)}$$

$$If (R_f + R_s) << R_L$$

$$\eta = \frac{4}{\pi^2} \cdot \frac{2}{1} = \frac{8}{\pi^2} = 0.812 = 81.2\%$$

ix) Transformer Utilization Factor (TUF):

The d.c. power to be delivered to the load in a rectifier circuit decides the rating of the transformer used in the circuit. So, transformer utilization factor is defined as

a) TUF (Secondary) =

$$\frac{P_{de} \text{ delivered to load}}{AC \text{ power rating of transformer secondary}}$$

b) Since both the windings are used TUF FWR = 2 TUF HWR

= 2 x 0.287 = 0.574

c) TUF primary = Rated efficiency =  $\frac{P_{de}}{P_{ac}} \times 100 = 81.2\%$

d) Average =  $\frac{0.812 + 0.574}{0.812 + 0.574} = 0.693$

2

#### x) Peak Inverse Voltage (PIV):

It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction. The peak inverse voltage across a diode is the peak of the negative half- cycle. For half- wave rectifier, PIV is 2Vm

xi) % Regulation

Voltage regulation =

=

$$\frac{I_{dc}(R_s + R_f)}{\frac{2V_m}{\pi} - I_{DC}(R_f + R_S)}$$

#### Advantages

1) Ripple factor = 0.482 (against 1.21 for HWR)

2) Rectification efficiency is 0.812 (against 0.405 for HWR)

3) Better TUF (secondary) is 0.574 (0.287 for HWR)

4) No core saturation problem

Disadvantages:

1) Requires center tapped transformer.

# BRIDGE RECTIFIER.

Another type of circuit that produces the same output waveform as the full wave rectifier circuit

roots to success.

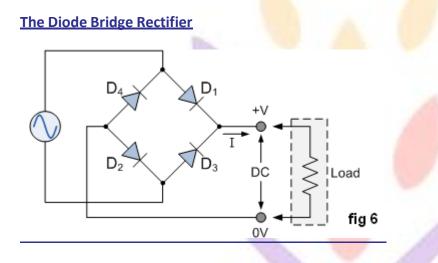

above, is that of the **Full Wave Bridge Rectifier**. This type of single phase rectifier uses four individual rectifying diodes connected in a closed loop "bridge" configuration to produce the desired output. The main advantage of this bridge circuit is that it does not require a special centre tapped transformer, thereby reducing its size and cost. The single secondary winding is connected to one side of the diode bridge network and the load to the other side as shown below.

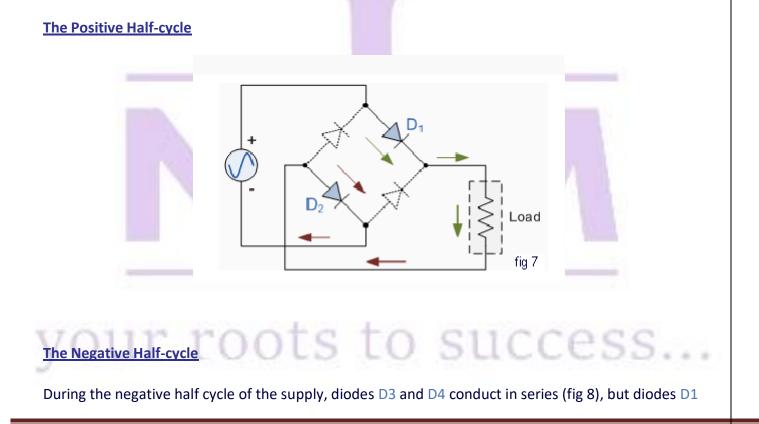

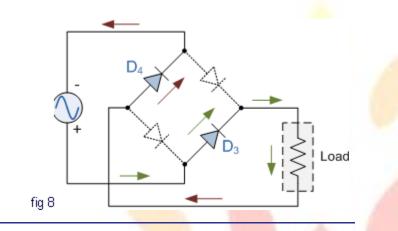

The four diodes labelled  $D_1$  to  $D_4$  are arranged in "series pairs" with only two diodes conducting currentduring each half cycle. During the positive half cycle of the supply, diodes D1 and D2 conduct in series while diodes D3 and D4 are reverse biased and the current flows through the load as shown below (fig 7).

and D2 switch "OFF" as they are now reverse biased. The current flowing through the load is the same direction as before.

As the current flowing through the load is unidirectional, so the voltage developed across the load is

also unidirectional the same as for the previous two diode full-wave rectifier, therefore the average DC

voltage across the load is  $0.637V_{max}$ . However in reality, during each half cycle the current flows through two diodes instead of just one so the amplitude of the output voltage is two voltage drops (2x 0.7 = 1.4V) less than the input V<sub>MAX</sub> amplitude. The ripple frequency is now twice the supply frequency (e.g. 100Hz for a 50Hz supply)

Therefore, the following expressions are same as that of full wave rectifier.

- a) Average current  $I_{dc} = \frac{2I_m}{\pi}$

- b) RMS current  $I_{\rm rms} = \frac{I_m}{\sqrt{2}}$

- c) DC output voltage (no.load)  $V_{DC} \frac{2V_m}{\pi}$

- d) Ripple factor  $\gamma = 0.482$

- e) Rectification efficiency =  $\eta = 0.812$

- f) DC output voltage full load.

=

$$V_{DCFL} = \frac{2V_m}{\pi} - I_{de}(R_s + 2R_f)$$

; i.e., less by one diode loss.

TUF of both primary & secondary are 0.812 therefore TUF overall is 0.812 (better than FWR with 0.693)

# your roots to success...

#### **Comparison:**

| SL<br>No. | Parameter                       | HWR                                   | FWR                          | BR                           |

|-----------|---------------------------------|---------------------------------------|------------------------------|------------------------------|

| 1         | No. of diodes                   | 1                                     | 2                            | 4                            |

| 2         | PIV of diodes                   | Vm                                    | 2 V <sub>m</sub>             | Vm                           |

| 3         | Secondary voltage (rms)         | V                                     | V-0-V                        | V                            |

| 4         | DC output voltage at no load    | $\frac{V_m}{\pi} = 0.318 \text{ V}_m$ | $\frac{2V_m}{\pi}$ =0.636 Vm | $\frac{2V_m}{\pi}$ =0.636 Vm |

| 5         | Ripple factor y                 | 1.21                                  | 0.482                        | 0.482                        |

| 6         | Ripple frequency                | f                                     | 2f                           | 2f                           |

| 7         | Rectification efficiency $\eta$ | 0,406                                 | 0.812                        | 0.812                        |

| 8         | TUF                             | 0.287                                 | 0.693                        | 0.812                        |

#### **FILTERS**

The output of a rectifier contains dc component as well as ac component. Filters are used to minimize the undesirable ac i.e., ripple leaving only the dc component to appear at the output.

Some important filters are:

- 1. Inductor filter

- 2. Capacitor filter

- 3. LC or L section filter

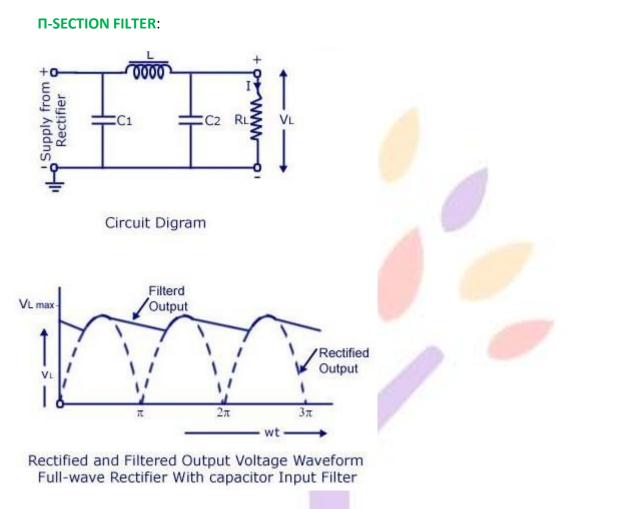

- 4. CLC or Π-type filter

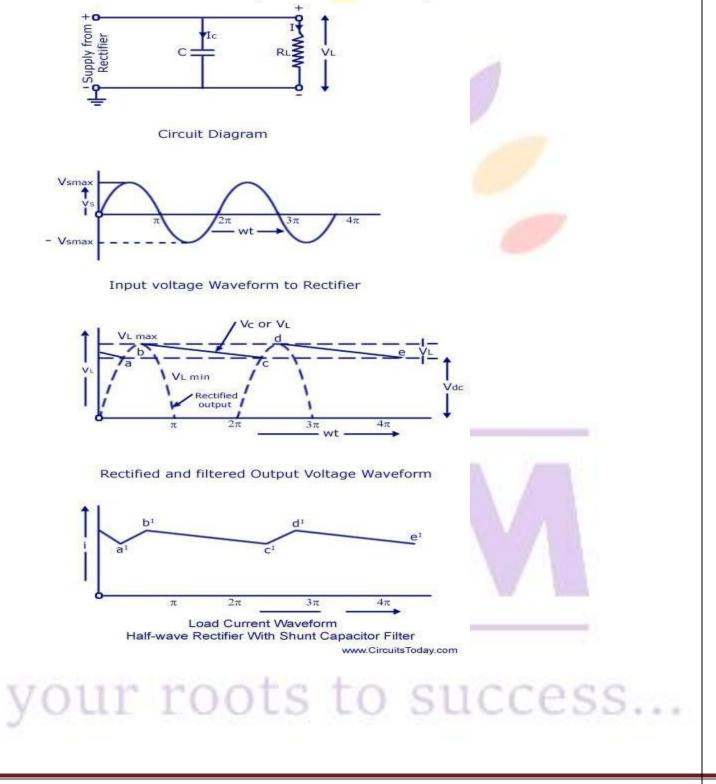

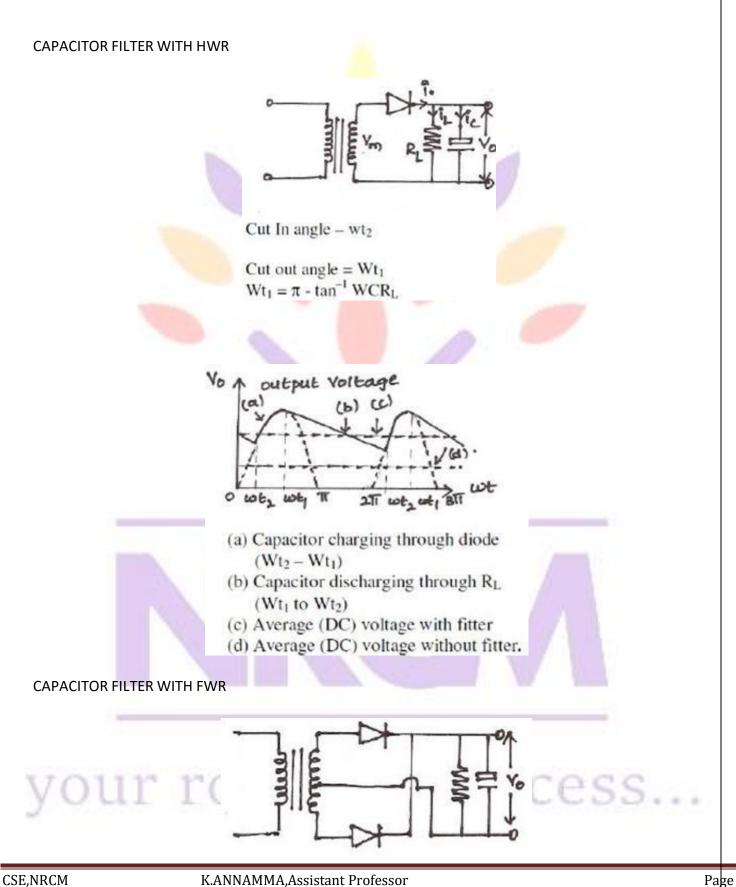

#### **CAPACITOR FILTER**

This is the most simple form of the <u>filter circuit</u> and in this arrangement a high value capacitor C is placed directly across the output terminals, as shown in figure. During the conduction period it gets charged and stores up energy to it during non-conduction period. Through this process, the time duration during which Ft is to be noted here that the capacitor C gets charged to the peak because there is no resistance (except the negligible forward resistance of diode) in the charging path. But the discharging time is quite large (roughly 100 times more than the charging time depending upon the value of RL) because it discharges through load resistance RL.

The function of the capacitor filter may be viewed in terms of impedances. The large value capacitor C offers a low impedance shunt path to the ac components or ripples but offers high impedance to the

dc component. Thus ripples get bypassed through capacitor C and only dc component flows through the load resistance RL

Capacitor filter is very popular because of its low cost, small size, light weight and good characteristics.

K.ANNAMMA, Assistant Professor

Page 56

#### The worthnoting points about shunt capacitor filter are:

1.For a fixed-value filter capacitance larger the load resistance RL larger will be the discharge time constant CRL and therefore, lower the ripples and more the output voltage. On the other hand lower the load resistance (or more the load current), lower will be the output voltage.

2.Similarly smaller the filter capacitor, the less charge it can hold and more it will discharge. Thus the peak-to-peak value of the ripple will increase, and the average dc level will decrease. Larger the filter capacitor, the more charge it can hold and the less it will discharge. Hence the peak-to-peak value of the ripple will be less, and the average dc level will increase. But, the maximum value of the capacitance that can be employed is limited by another factor. The larger the capacitance value, the greater is the current required to charge the capacitor to a given voltage. The maximum current that can be handled by a diode is limited by the figure quoted by the manufacturer. Thus the maximum value of the capacitance, that can be used in the shunt filter capacitor is limited.

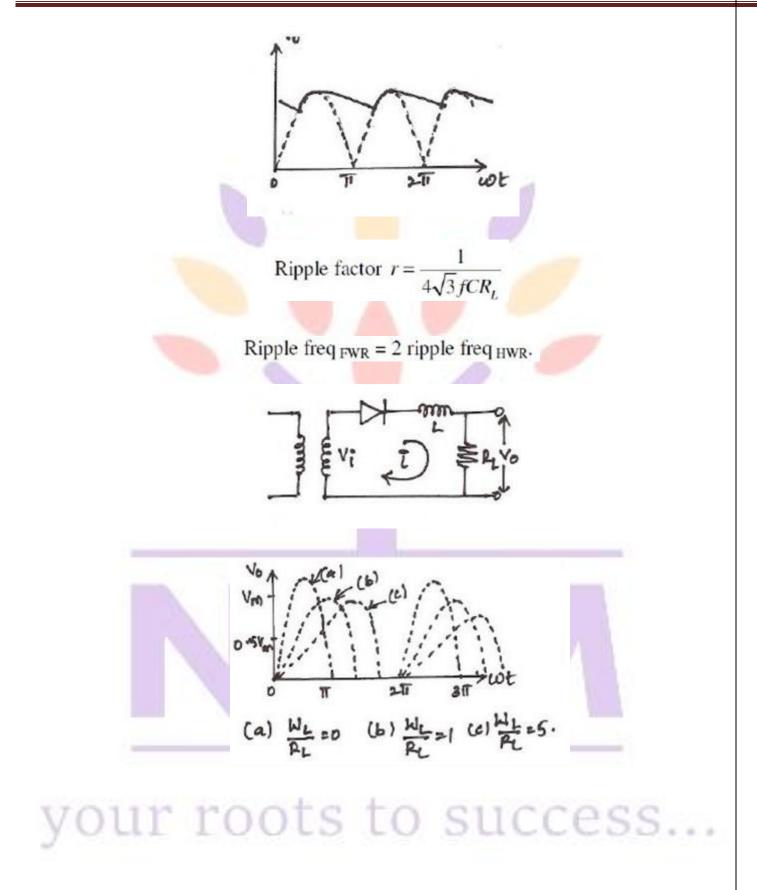

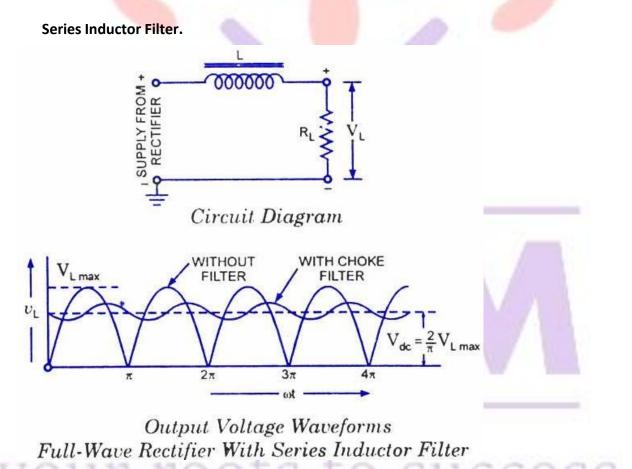

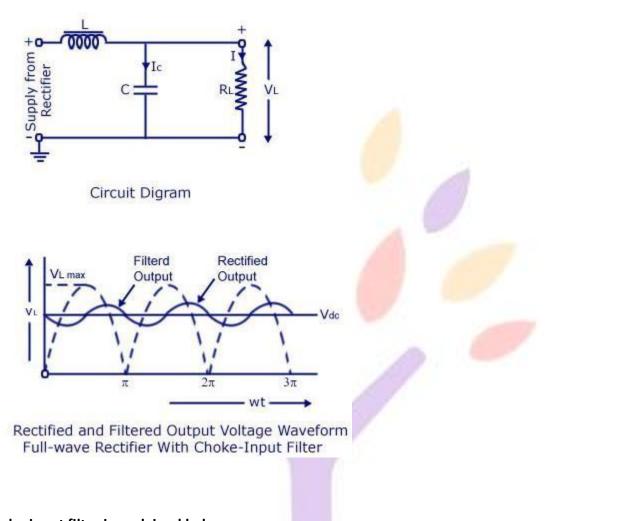

In this arrangement a high value inductor or choke L is connected in series with the rectifier element and the load, as illustrated in figure. The filtering action of an inductor filter depends upon its property of opposing any change in the current flowing through it. When the output current of the rectifier

increases above a certain value, energy is stored in it in the form of magnetic field and this energy is given up when the output current falls below the average value. Thus by placing a choke coil in series with the rectifier output and load, any sudden change in current that might have occurred in the circuit without an inductor is smoothed out by the presence of the inductor L.

The function of the inductor filter may be viewed in terms of impedances. The choke offers high impedance to the ac components but offers almost zero resistance to the desired dc components. Thus ripples are removed to a large extent. Nature of the output voltage without filter and with choke filter is shown in figure.

For dc (zero frequency), the choke resistance  $R_c$  in series with the load resistance  $R_L$  forms a voltage divider and dc voltage across the load is given as

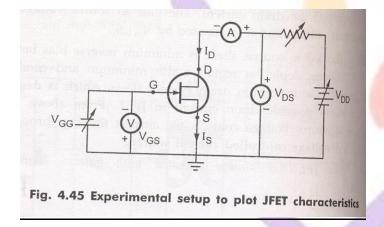

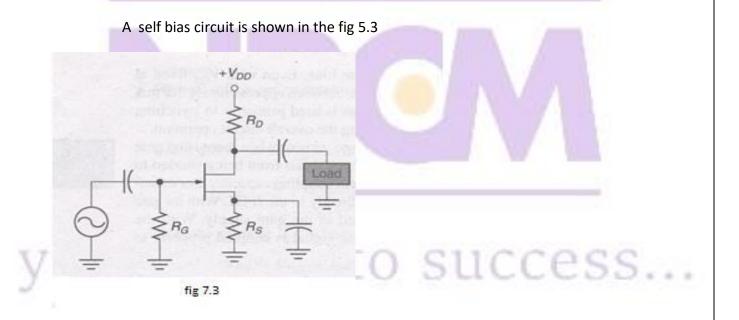

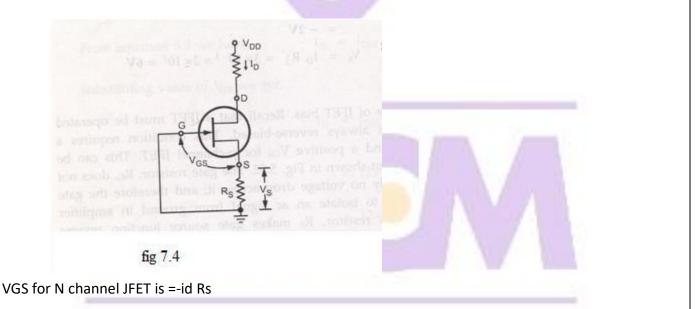

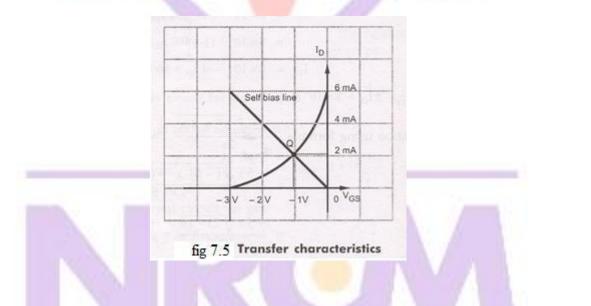

where V<sub>dc</sub> is dc voltage output from a full-wave rectifier. Usually choke coil resistance Rc, is much small than R<sub>L</sub> and, therefore, almost entire of the dc voltage is available across the load resistance R<sub>L</sub>.